相較三星5納米(nm)而言,優(yōu)化的3納米(nm)工藝,性能提高23%,功耗降低45%,芯片面積減少16%

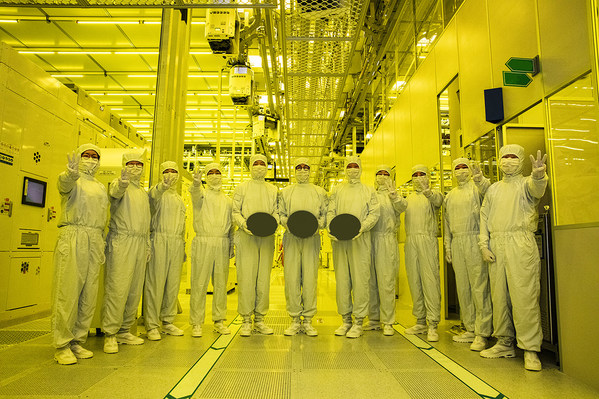

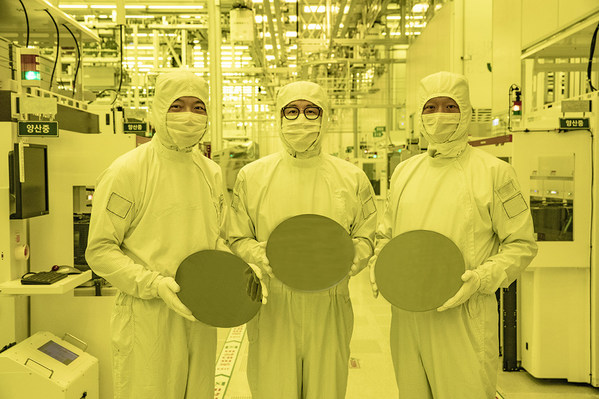

2022年6月30日,作為先進(jìn)的半導(dǎo)體技術(shù)廠(chǎng)商之一的三星電子今日宣布, 基于3納米(nm)全環(huán)繞柵極(Gate-All-AroundT,簡(jiǎn)稱(chēng) GAA)制程工藝節(jié)點(diǎn)的芯片已經(jīng)開(kāi)始初步生產(chǎn)。

三星電子首次實(shí)現(xiàn)GAA"多橋-通道場(chǎng)效應(yīng)晶體管"(簡(jiǎn)稱(chēng): MBCFET TM Multi-Bridge-Channel FET)應(yīng)用打破了FinFET技術(shù)的性能限制,通過(guò)降低工作電壓水平來(lái)提高能耗比,同時(shí)還通過(guò)增加驅(qū)動(dòng)電流增強(qiáng)芯片性能。三星首先將納米片晶體管應(yīng)用于高性能、低功耗計(jì)算領(lǐng)域的半導(dǎo)體芯片,并計(jì)劃將其擴(kuò)大至移動(dòng)處理器領(lǐng)域。

三星電子Foundry業(yè)務(wù)部總經(jīng)理崔時(shí)榮表示:"一直以來(lái),三星電子不斷將新一代工藝技術(shù)應(yīng)用于生產(chǎn)制造中。例如:三星的第一個(gè)High-K Metal Gate (HKMG) 工藝、FinFET 以及 EUV等。三星希望通過(guò)率先采用3nm工藝的"多橋-通道場(chǎng)效應(yīng)晶體管"( MBCFETTM),將繼續(xù)保持半導(dǎo)體行業(yè)前沿地位。同時(shí),三星將繼續(xù)在競(jìng)爭(zhēng)性技術(shù)開(kāi)發(fā)方面積極創(chuàng)新,并建立有助于加速實(shí)現(xiàn)技術(shù)成熟的流程"。

技術(shù)設(shè)計(jì)優(yōu)化,使PPA[1]收益更大化

3nmGAA 技術(shù)采用了更寬通的納米片,與采用窄通道納米線(xiàn)的GAA 技術(shù)相比能提供更高的性能和能耗比。3納米GAA 技術(shù)上,三星能夠調(diào)整納米晶體管的通道寬度,優(yōu)化功耗和性能,從而能夠滿(mǎn)足客戶(hù)的多元需求。此外,GAA 的設(shè)計(jì)靈活性對(duì)設(shè)計(jì)技術(shù)協(xié)同優(yōu)化(DTCO) [2]非常有利,有助于實(shí)現(xiàn)更好的PPA 優(yōu)勢(shì)。與三星5nm工藝相比,第一代3nm工藝可以使功耗降低45%,性能提升23%,芯片面積減少16%;而未來(lái)第二代3nm工藝則使功耗降低50%,性能提升30%,芯片面積減少 35%。

與SAFETM合作伙伴一起,提供3納米設(shè)計(jì)基礎(chǔ)設(shè)施和服務(wù)

隨著工藝節(jié)點(diǎn)變得越來(lái)越小,而芯片性能需求越來(lái)越高,IC設(shè)計(jì)師們需要面對(duì)處理海量數(shù)據(jù),以及驗(yàn)證功能更多、擴(kuò)展更緊密的復(fù)雜產(chǎn)品的挑戰(zhàn)。為了滿(mǎn)足這些需求,三星致力于提供更穩(wěn)定的設(shè)計(jì)環(huán)境,以幫助減少設(shè)計(jì)、驗(yàn)證和批準(zhǔn)過(guò)程所需的時(shí)間,同時(shí)也提高了產(chǎn)品的可靠性。

自2021年第三季度以來(lái),三星電子一直通過(guò)與包括ANSYS、楷登電子、西門(mén)子和新思科技在內(nèi)的三星先進(jìn)晶圓代工生態(tài)系統(tǒng)SAFE TM(Samsung Advanced Foundry Ecosystem)合作伙伴的緊密協(xié)作,提供成熟的設(shè)計(jì)基礎(chǔ)設(shè)施,使其能夠在更短的時(shí)間內(nèi)完善其產(chǎn)品。

關(guān)于三星

三星以創(chuàng)新理念和技術(shù)激勵(lì)世界,塑造未來(lái)。三星正致力于定義電視、智能手機(jī)、可穿戴設(shè)備、平板電腦、數(shù)字家電、網(wǎng)絡(luò)系統(tǒng)以及內(nèi)存、系統(tǒng)LSI、芯片代工和LED解決方案的世界。

欲知最新消息,請(qǐng)?jiān)L問(wèn)并關(guān)注三星半導(dǎo)體微信(三星半導(dǎo)體和顯示官方)和微博(三星半導(dǎo)體)平臺(tái)。

來(lái)自SAFETM合作伙伴

ANSYS, [John Lee, Ansys電子、半導(dǎo)體和光學(xué)業(yè)務(wù)部副總裁兼總經(jīng)理]

"ANSYS和三星攜手合作,使用3nm GAA技術(shù)繼續(xù)為最先進(jìn)的設(shè)計(jì)提供支持技術(shù)。目前,Ansys多物理場(chǎng)仿真平臺(tái)的簽核精度,保證了我們與行業(yè)前沿地位的三星晶圓代工持續(xù)合作伙伴關(guān)系。Ansys始終致力于為我們共同的重要客戶(hù)提供最佳的設(shè)計(jì)體驗(yàn)。"

楷登電子, [Tom Beckley,楷登電子定制IC和PCB部門(mén)高級(jí)副總裁兼總經(jīng)理]

"楷登電子祝賀三星實(shí)現(xiàn)了3nm GAA技術(shù)工藝節(jié)點(diǎn)的生產(chǎn)這一行業(yè)里程碑。我們與三星晶圓代工密切合作,讓客戶(hù)能夠通過(guò)使用我們的數(shù)字解決方案實(shí)現(xiàn)3nm GAA技術(shù)工藝節(jié)點(diǎn)的最佳功率、性能和尺寸。從數(shù)據(jù)描述到全數(shù)字流程實(shí)施和簽名,所有這些都基于Cadence Cerebrus AI的技術(shù)驅(qū)動(dòng),以最大限度地提高生產(chǎn)率。通過(guò)定制解決方案,我們與三星共同啟用并驗(yàn)證了完整的AMS流程,通過(guò)自動(dòng)化布局提高了電路設(shè)計(jì)和模擬的生產(chǎn)效率。我們期待著繼續(xù)以這樣的合作,取得更大的成功。"

西門(mén)子 EDA, [Joe Sawicki, 西門(mén)子EDA IC 部門(mén)執(zhí)行副總裁]

"西門(mén)子EDA很高興通過(guò)與三星的合作,從最初開(kāi)發(fā)階段確保我們現(xiàn)有的軟件平臺(tái)也能夠在三星新的3納米(nm)工藝節(jié)點(diǎn)上運(yùn)行。通過(guò)SAFETM計(jì)劃,西門(mén)子行業(yè)領(lǐng)先的3nm EDA工具得已認(rèn)證,我們與三星的長(zhǎng)期合作也為我們的共同客戶(hù)創(chuàng)造了巨大的價(jià)值。與三星建立了長(zhǎng)期的伙伴關(guān)系,為我們的共同客戶(hù)創(chuàng)造了重大價(jià)值。"

新思科技, [ Shankar Krishnamoorthy, 新思科技芯片實(shí)現(xiàn)事業(yè)部總經(jīng)理]

"通過(guò)我們與三星代工事業(yè)部的長(zhǎng)期戰(zhàn)略合作,使得我們的解決方案能夠支持三星的先進(jìn)工藝,幫助我們共同的客戶(hù)加快他們的設(shè)計(jì)周期。現(xiàn)在通過(guò)新思科技數(shù)字設(shè)計(jì)、模擬設(shè)計(jì)和IP產(chǎn)品,繼續(xù)擴(kuò)大對(duì)三星采用GAA架構(gòu)的3nm工藝的支持,使客戶(hù)能夠?yàn)殛P(guān)鍵的高性能計(jì)算應(yīng)用提供差異化的SoC。

*本文中的產(chǎn)品圖片以及型號(hào)、數(shù)據(jù)、功能、性能、規(guī)格參數(shù)等僅供參考,三星有可能對(duì)上述內(nèi)容進(jìn)行改進(jìn),具體信息請(qǐng)參照產(chǎn)品實(shí)物、產(chǎn)品說(shuō)明書(shū)或三星官網(wǎng)。除非經(jīng)特殊說(shuō)明,本網(wǎng)站中所涉及的數(shù)據(jù)均為三星內(nèi)部測(cè)試結(jié)果,涉及的對(duì)比均為與三星產(chǎn)品相比較。